# TLE7259-2GE

LIN Transceiver

**Automotive Power**

#### **Table of Contents**

# **Table of Contents**

| 1                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                     | 3                                                        |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2                                                                                                     | Block Diagram                                                                                                                                                                                                                                                                                                                | 4                                                        |

| <b>3</b><br>3.1<br>3.2                                                                                | Pin Configuration         Pin Assignment         Pin Definitions and Functions                                                                                                                                                                                                                                               | 5                                                        |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | Functional Description Operating Modes Normal Operation Mode Normal Slope Mode Flash Mode Stand-By Mode Sleep Mode Wake-Up Events Bus Wake-Up via LIN bus Local Wake-Up Mode Transition via EN pin TxD Time Out function Over Temperature protection 3.3 V and 5 V Logic Capability LIN Specifications 1.2, 1.3, 2.0 and 2.1 | 10<br>10<br>10<br>11<br>12<br>12<br>13<br>14<br>15<br>15 |

| <b>5</b><br>5.1<br>5.2<br>5.3                                                                         | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Characteristics                                                                                                                                                                                                                            | 17<br>18                                                 |

| <b>6</b><br>6.1<br>6.2                                                                                | Electrical Characteristics  Functional Device Characteristics  Diagrams                                                                                                                                                                                                                                                      | 19                                                       |

| <b>7</b> 7.1 7.2 7.3 7.4 7.5                                                                          | Application Information  ESD Robustness according to IEC61000-4-2  Pin Compatibility to other LIN Transceivers  Master Termination  External Capacitors  Application Example                                                                                                                                                 | 25<br>25<br>26<br>26                                     |

| 8                                                                                                     | Package Outlines                                                                                                                                                                                                                                                                                                             | 29                                                       |

| 9                                                                                                     | Revision History                                                                                                                                                                                                                                                                                                             | 30                                                       |

LIN Transceiver TLE7259-2GE

#### 1 Overview

#### **Features**

- Single-wire transceiver, pin compatible to the TLE7259-2GU

- Transmission rate up to 20 kBaud

- · Compliant to LIN specification 1.3, 2.0 and 2.1

- Very high ESD robustness, +/- 11 kV according to IEC61000-4-2

- Optimized for low electromagnetic emission (EME)

- Optimized for high immunity against electromagnetic interference (EMI)

- Very low current consumption in sleep mode with Wake-Up functions

- Wake-Up source detection

- Very low leakage current on the BUS output

- Digital I/O levels compatible for 3.3 V and 5 V microcontrollers

- Suitable for 12 V and 24 V board net

- Bus short to V<sub>BAT</sub> protection and Bus short to GND handling

- Over temperature protection and Under voltage detection

- · Flash mode

- Green Product (RoHs compliant)

- AEC Qualified

PG-DSO-8

#### Description

The TLE7259-2GE is a transceiver for the Local Interconnect Network (LIN) with integrated Wake-Up and protection features. It is designed for in-vehicle networks using data transmission rates from 2.4 kBaud to 20 kBaud. The TLE7259-2GE functions as a bus driver between the protocol controller and the physical bus inside the LIN network. Compliant to all LIN standards and with a wide operational supply range the TLE7259-2GE can be used in all automotive applications.

Different operation modes and the INH output allow the TLE7259-2GE to control external components, like voltage regulators. In Sleep-mode the TLE7259-2GE draws less than 8  $\mu$ A of quiescent current while still being able to wake up off of LIN bus traffic and a local Wake-Up input. The very low leakage current on the BUS pin makes the TLE7259-2GE especially suitable for partially supplied networks and supports the low quiescent current requirements of the LIN network.

Based on the Infineon Smart Power Technology SPT®, the TLE7259-2GE provides excellent ESD Robustness together with a very high electromagnetic immunity (EMI). The TLE7259-2GE reaches a very low level of electromagnetic emission (EME) within a broad frequency range and independent from the battery voltage.

The Infineon Smart Power Technology SPT® allows bipolar and CMOS control circuitry in accordance with DMOS power devices existing on the same monolithic circuit. The TLE7259-2GE and the Infineon SPT® technology are AEC qualified and tailored to withstand the harsh condition of the Automotive Environment.

| Туре        | Package  | Marking  |

|-------------|----------|----------|

| TLE7259-2GE | PG-DSO-8 | 7259-2GE |

Data Sheet 3 Rev. 1.0, 2007-11-12

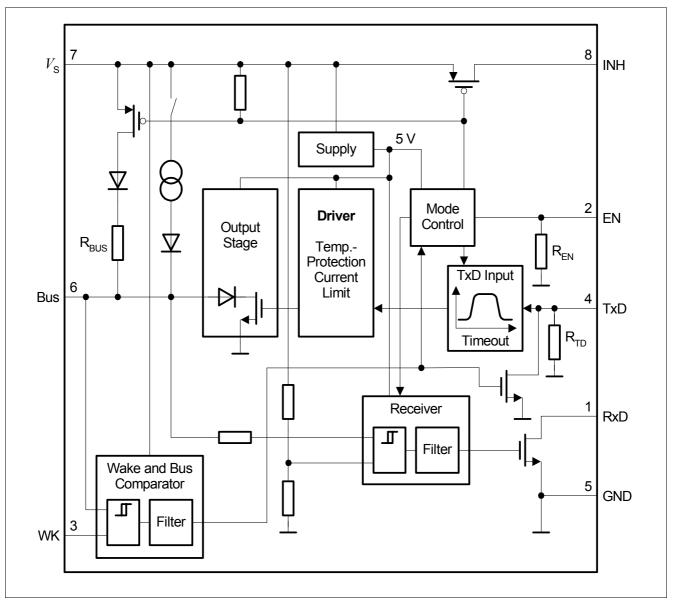

**Block Diagram**

# 2 Block Diagram

Figure 1 Block Diagram

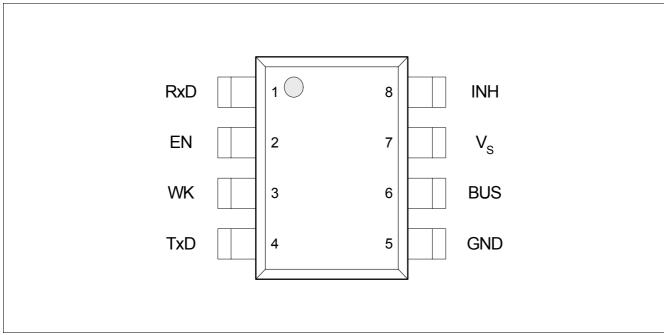

**Pin Configuration**

# 3 Pin Configuration

### 3.1 Pin Assignment

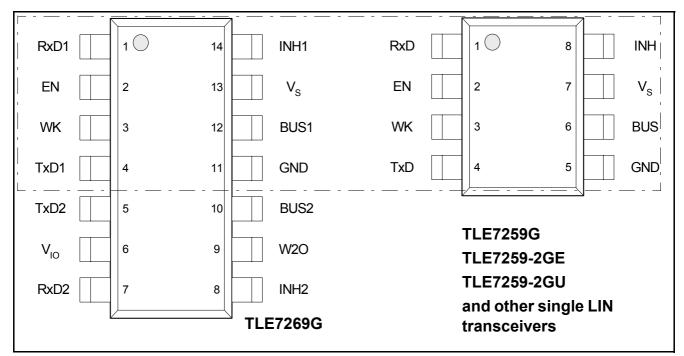

Figure 2 Pin Configuration

Note: The pin configuration of the TLE7259-2GE is pin compatible to the devices TLE7259G, TLE7259-2GU and the Twin LIN Transceiver TLE7269G. In comparison to the TLE7269G, the TLE 7259-2GE has no separate  $V_{\rm IO}$  power supply and needs a pull up resistor at the RxD pin. Details can be found inside the chapter "Pin Compatibility to other LIN Transceivers" on Page 25.

#### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                         |

|-----|--------|----------------------------------------------------------------------------------|

| 1   | RxD    | Receive data output;                                                             |

|     |        | External Pull Up necessary                                                       |

|     |        | LOW in dominant state, active LOW after a Wake-Up event at BUS or WK pin         |

| 2   | EN     | Enable input;                                                                    |

|     |        | integrated pull-down, device set to normal operation mode when HIGH              |

| 3   | WK     | Wake input;                                                                      |

|     |        | active LOW, negative edge triggered, internal pull-up                            |

| 4   | TxD    | Transmit data input;                                                             |

|     |        | integrated pull-down, LOW in dominant state; active LOW after Wake-Up via WK pin |

| 5   | GND    | Ground                                                                           |

| 6   | BUS    | Bus input / output;                                                              |

|     |        | LIN bus line input / output                                                      |

|     |        | LOW in dominant state                                                            |

|     |        | Internal termination and pull-up current source                                  |

### **Pin Configuration**

| Pin | Symbol  | Function                                                                              |

|-----|---------|---------------------------------------------------------------------------------------|

| 7   | $V_{S}$ | Battery supply input                                                                  |

| 8   | INH     | Inhibit output;                                                                       |

|     |         | battery supply related output                                                         |

|     |         | $HIGH\ (V_{S})$ in Normal and Stand-By operation mode                                 |

|     |         | can be used to control an external voltage regulator                                  |

|     |         | can be used to control external bus termination resistor when the device will be used |

|     |         | as Master node                                                                        |

### 4 Functional Description

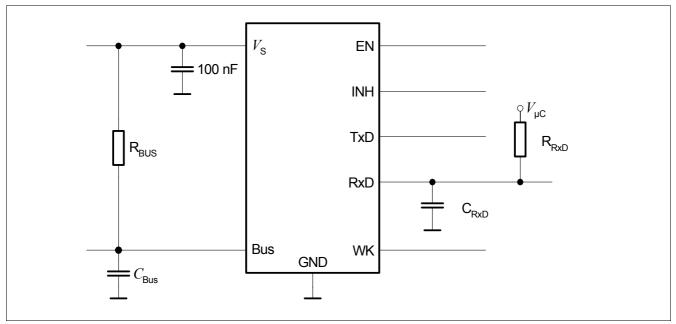

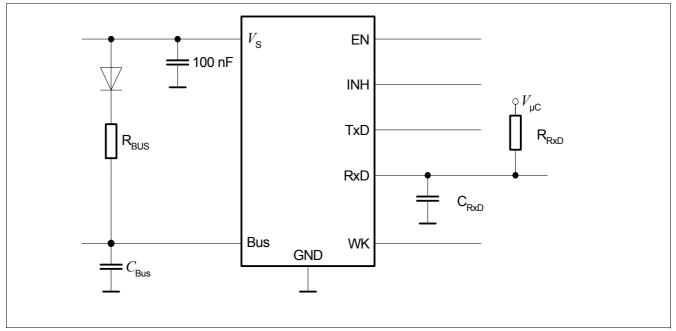

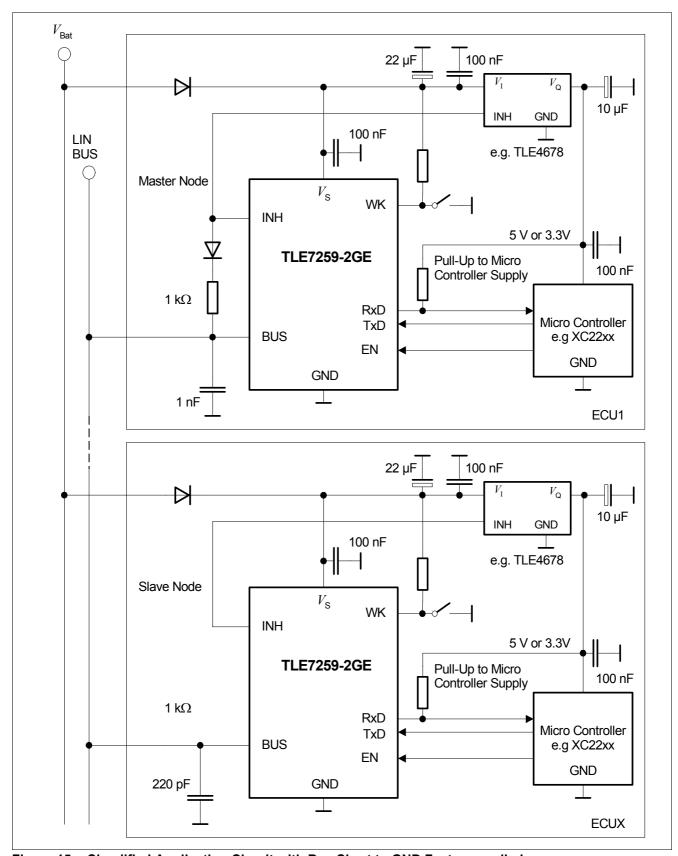

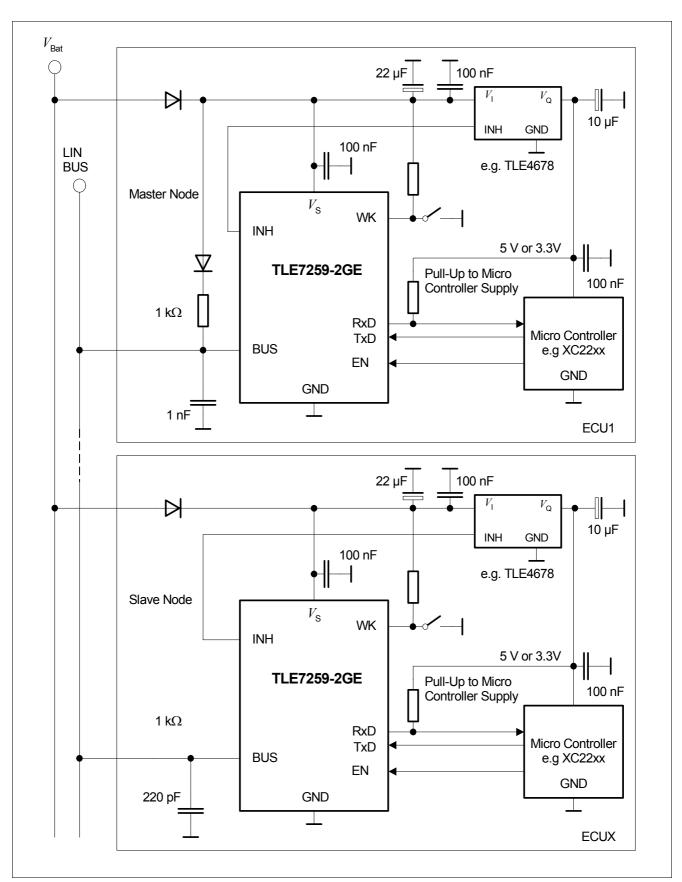

The LIN Bus is a single wire, bi-directional bus, used for in-vehicle networks. The LIN Transceiver TLE7259-2GE is the interface between the microcontroller and the physical LIN Bus (see **Figure 15** and **Figure 16**). The logical values of the microcontroller are driven to the LIN bus via the TxD input of the TLE7259-2GE. The transmit data stream on the TxD input is converted to a LIN bus signal with optimized slew rate to minimize the EME level of the LIN network. The RxD output reads back the information from the LIN bus to the microcontroller. The receiver has an integrated filter network to suppress noise on the LIN Bus and to increase the EMI (Electro Magnetic Immunity) level of the transceiver.

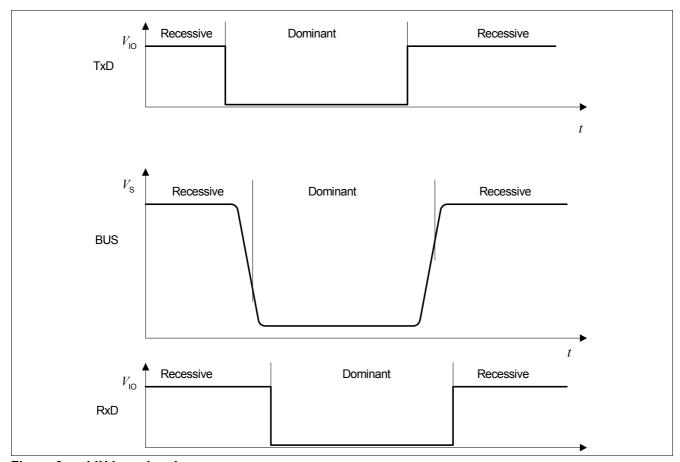

Two logical states are possible on the LIN bus according to the LIN Specification 2.1 (see Figure 3):

In dominant state, the voltage on the LIN bus is set to the GND level. In recessive state, the voltage on the LIN bus is set to the supply voltage  $V_{\rm S}$ . By setting the TxD input of the TLE7259-2GE to "Low" the transceiver generates a dominant level on the BUS interface pin. The RxD output reads back the signal on the LIN bus and indicates a dominant LIN bus signal with a logical "Low" to the microcontroller. Setting the TxD pin to "High" the transceiver TLE7259-2GE sets the LIN interface pin BUS to the recessive level, at the same time the recessive level on the LIN bus is indicated by a logical "High" on the RxD output.

Every LIN network consists of a master node and one or more slave nodes. To configure the TLE7259-2GE for master node applications, a resistor in the range of 1 k $\Omega$  and a reverse diode must be connected between the LIN bus and the power supply  $V_S$  or the INH pin of the TLE7259-2GE (see **Figure 15** and **Figure 16**).

Figure 3 LIN bus signals

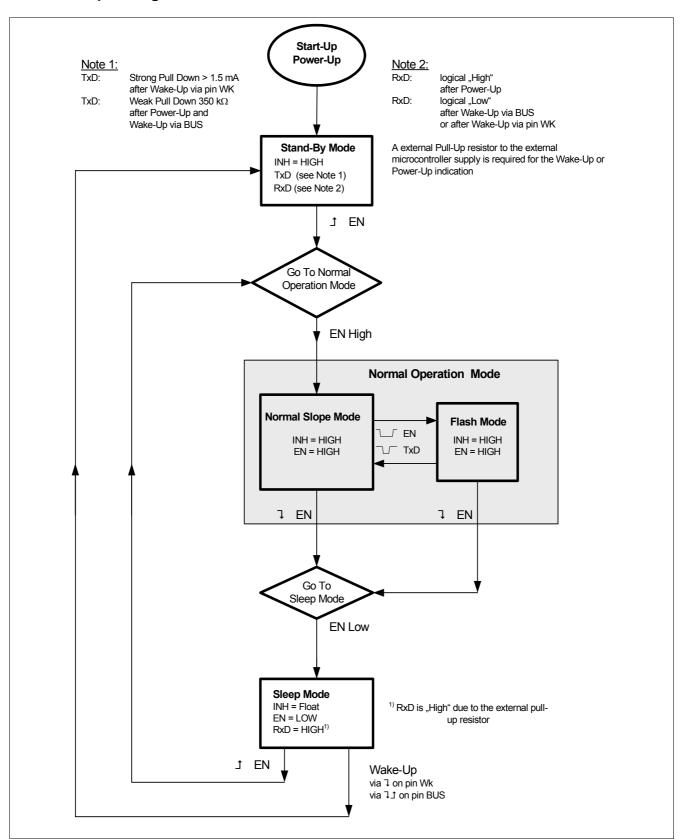

### 4.1 Operating Modes

Figure 4 Operation Mode State Diagram

The TLE7259-2GE has 3 major operation modes:

- · Stand-By mode

- Normal Operation mode

- Sleep mode

The Normal Operation mode contains 2 sub-operation modes, which differentiate by the slew rate control of the LIN Bus signal (see **Figure 4**).

Sub-operation modes with different slew rates on the BUS pin:

- Normal Slope mode, for data transmission rates up to 20 kBaud

- Flash mode, for programming of the external microcontroller

The operation mode of the TLE7259-2GE is selected by the EN pin. (see Figure 4).

Table 1 Operating modes

| Mode                | EN   | INH      | TxD                       | RxD                       | LIN Bus<br>Termination | Comments                                                                                                                                                                                                                            |

|---------------------|------|----------|---------------------------|---------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep               | Low  | Floating | Low                       | High <sup>1)</sup>        | High<br>Impedance      | No wake-up request detected                                                                                                                                                                                                         |

| Stand-By            | Low  | High     | Low<br>High <sup>2)</sup> | Low<br>High <sup>1)</sup> | 30 kΩ<br>(typical)     | RxD "Low" after local Wake-Up (pin WK) or bus Wake-Up (pin BUS) RxD "High" after Power-Up TxD strong pull down after local Wake-Up (WK pin) <sup>2)</sup> TxD weak pull down after bus Wake-Up ( pin BUS) or Power-Up <sup>2)</sup> |

| Normal<br>Operation | High | High     | Low<br>High               | Low<br>High               | 30 kΩ<br>(typical)     | RxD reflects the signal on the BUS TxD driven by the microcontroller                                                                                                                                                                |

<sup>1)</sup> A pull-up resistor to the external microcontroller supply is required.

#### 4.2 Normal Operation Mode

The TLE7259-2GE enters the Normal Operation mode after the microcontroller sets EN to "High" (see **Figure 4**). In Normal Operation mode the LIN bus receiver and the LIN bus transmitter are active. Data from the microcontroller is transmitted to the LIN bus via the TxD pin, the receiver detects the data stream on the LIN bus and forwards it to the RxD output pin. In Normal Operation mode, the INH pin is "High" (set to  $V_{\rm S}$ ) and the bus termination is set to 30 k $\Omega$ .

Normal Slope mode and the Flash mode are Normal Operation modes and in these sub-modes the behavior of the INH pin and the bus termination is the same. Per default the TLE7259-2GE always enters into Normal Slope mode, either from Sleep mode or from Stand-By mode. The Flash mode can only be entered from Normal Slope mode.

In order to avoid any bus disturbance during a mode change, the output stage of the TLE7259-2GE is disabled and set to recessive state during the mode change procedure. To release the TLE7259-2GE for data communication on the LIN bus, the TxD pin needs to be set to "High" for the time  $t_{\text{to.rec}}$ .

<sup>2)</sup> The TxD input needs an external termination to indicate a "High" or a "Low" signal. The external termination could be a pull-up resistor or an active microcontroller output.

#### 4.2.1 Normal Slope Mode

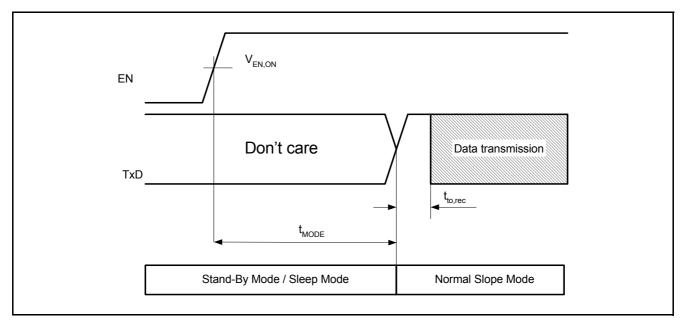

In Normal Slope mode data transmission rates up to 20 kBauds are possible. Setting the EN pin to "High" starts the transition to Normal Slope mode. (see **Figure 5**).

The mode change to Normal Slope mode is defined by the time  $t_{\text{MODE}}$ . The time  $t_{\text{MODE}}$  specifies the delay time between the threshold, where the EN pin detects a "High" input signal, and the actual mode change of TLE7259-2GE into Normal Slope mode. Entering in Normal Operation mode, the TLE7259-2GE always enters per default into Normal Slope mode. The signal on the TxD pin is not relevant for entering into Normal Slope mode.

Finally to release the data communication it is required to set the TxD pin to "High" for the time  $t_{\rm to,rec.}$

Figure 5 Timing to enter Normal Slope Mode

#### 4.2.2 Flash Mode

In Flash mode it is possible to transmit and receive LIN messages on the LIN bus. The slew rate control mechanism of the LIN bus signal is disabled. This allows higher data transmission rates, disregarding the EMC limitations of the LIN network. The Flash mode is intended to be used during the ECU production for programming the microcontroller via the LIN bus interface.

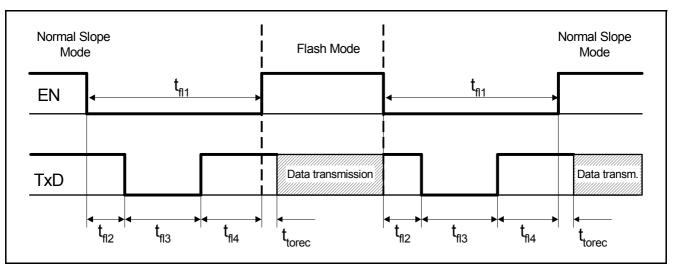

The TLE7259-2GE can be set to Flash mode only from Normal Slope mode (see **Figure 4**). Flash mode is entered by setting the EN pin to "Low" for the time  $t_{\rm fl1}$  and generating a falling and a rising edge at the TxD pin with the timing  $t_{\rm fl2}$ ,  $t_{\rm fl3}$  and  $t_{\rm fl4}$  (see **Figure 6**). Leaving the Flash mode by the same sequence, sets the TLE7259-2GE back to Normal Slope mode. Finally to release the data transmission it is required to set the TxD pin to "High" for the time  $t_{\rm to,rec}$ .

Additionally the TLE7259-2GE can leave the Flash mode as well by switching only the EN pin to "Low". By applying this "Low" signal to the EN pin the TLE7259-2GE is put into Sleep mode.

Figure 6 Timing to enter and leave Flash Mode

#### 4.3 Stand-By Mode

The Stand-By mode is entered automatically after:

- A Power-Up event at the supply  $V_{\rm S}$ .

- · A bus Wake-Up event at the pin BUS.

- · A local Wake-Up event at the pin WK.

- A power on reset caused by power supply V<sub>S</sub>

- In Stand-By mode the Wake-Up sources are monitored by the TxD and RxD pins.

In Stand-By mode no communication on the LIN Bus is possible. The output stage is disabled and the LIN Bus termination remains activated. The RxD and the TxD pin are used to indicate the Wake-Up source or a Power-Up event. The RxD pin remains "Low" after a local Wake-Up event on the pin WK and a bus Wake-Up event on the LIN bus. A Power-Up event is indicated by a logical "High" on the RxD pin. The signal on the TxD pin indicates the Wake-Up source, a weak pull-down signals a bus Wake-Up event on the LIN bus and a strong pull-down signals a local Wake-Up event caused by the WK pin (see **Table 1** and **Table 2**). In order to detect a Wake-Up event via the TxD pin, the external microcontroller output needs to provide a logical "High" signal. The Wake-Up flags indicating the Wake-Up source on the pins TxD and RxD are reset by changing the operation mode to Normal Operation mode.

The signal on the EN pin remains "Low" due to an internal pull-down resistor. Setting the EN pin to "High", by the microcontroller returns the TLE7259-2GE to Normal Operation mode. In Stand-By mode the INH output is switching to  $V_{\rm S}$ . The INH output can be used to control external devices like a voltage regulator.

Table 2 Logic table for wake up monitoring

|          | _                         |                           | •                 | _                 |                            |

|----------|---------------------------|---------------------------|-------------------|-------------------|----------------------------|

| power up | WK                        | BUS                       | RxD <sup>1)</sup> | TxD <sup>2)</sup> | Remarks                    |

| Yes      | 1                         | 1                         | 1                 | 1                 | No Wake-Up, Power-Up event |

| No       | Wake-<br>Up <sup>3)</sup> | 1                         | 0                 | 0                 | Wake via wake pin          |

| No       | 1                         | Wake-<br>Up <sup>4)</sup> | 0                 | 1                 | Wake via BUS               |

- 1) To indicate the Wake-Up sources via the RxD pin, a pull-up resistor to the external microcontroller supply is required.

- 2) The TxD input needs an external termination to indicate a "High" or a "Low" signal. The external termination could be a pull-up resistor or an active microcontroller output.

- 3) A local Wake-Up event is considered after a low signal on the pin WK (see Chapter 4.7).

- 4) A bus Wake-Up event is considered after a low to high transition on the LIN bus (see Chapter 4.6)

### 4.4 Sleep Mode

In order to reduce the current consumption the TLE7259-2GE offers a Sleep mode. In Sleep mode the quiescent current on  $V_{\rm S}$  and the leakage current on the pin BUS are cut back to a minimum.

To switch the TLE7259-2GE from Normal Operation mode to Sleep mode, the EN pin has to be set to "Low". Conversely a logical "High" on the EN pin sets the device directly back to Normal Operation mode (see **Figure 4**). While the TLE7259-2GE is in Sleep mode the following functions are available:

- The output stage is disabled and the internal bus terminations are switched off (High Impedance on the pin BUS). The internal current source on the bus pin ensures that the level on the pin BUS remains recessive and protects the LIN network against accidental bus Wake-Up events.

- · The receiver stage is turned off.

- RxD output pin is "High" if a pull-up resistor is connected to the external microcontroller supply. The TxD pin is disabled. The logical state on the TxD pin is "Low", due to the internal pull-down resistor.

- · The INH output is switched off and floating.

- The bus Wake-Up comparator is active and turns the TLE7259-2GE to Stand-By mode in case of a bus Wake-Up event.

- The WK pin is active and turns the TLE7259-2GE to Stand-By mode in case of a local Wake-Up.

- The EN pin remains active, switching the EN pin to "High" changes the operation mode to Normal Slope mode.

#### 4.5 Wake-Up Events

A Wake-Up event changes the operation mode of the TLE7259-2GE from Sleep mode to Stand-By mode. There are 3 different ways to wake-up the TLE7259-2GE from Sleep mode.

- Bus Wake-Up via a minimum dominant signal ( $t_{WK,bus}$ ) on the pin BUS.

- Local Wake-Up via a minimum dominant time ( $t_{WK}$ ) on the WK pin.

- Mode change from Sleep mode to Normal Operation mode, by setting the EN pin to logical "High".

#### 4.6 Bus Wake-Up via LIN bus

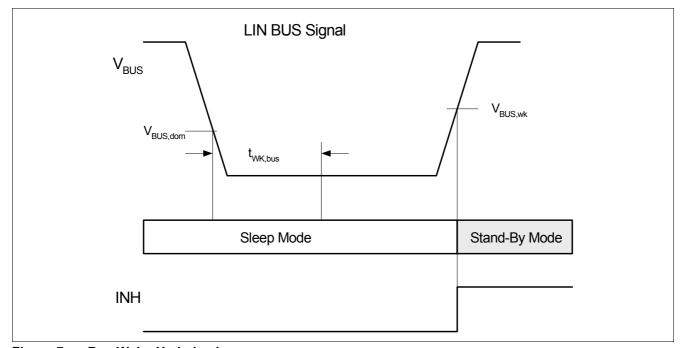

Figure 7 Bus Wake-Up behavior

The bus Wake-Up event, often called remote Wake-Up, changes the operation mode from Sleep mode to Stand-By mode. A falling edge on the LIN bus, followed by a dominant bus signal  $t > t_{WK,bus}$  results in a bus Wake-Up event. The mode change to Stand-By mode becomes active with the following rising edge on the LIN bus. The TLE7259-2GE remains in Sleep mode until it detects a change from dominant to recessive on the LIN bus (see Figure 7).

In Stand-By mode the TxD pin indicates the source of the Wake-Up event. A weak pull-down on the pin TxD indicates a bus Wake-Up event (see **Figure 4**). The RxD pin signals if a Wake-Up event occurred or the power-up event. A "Low" signal on the RxD pin reports a local or bus Wake-Up event, a logical "High" signal on RxD indicates a power-up event.

### 4.7 Local Wake-Up

Figure 8 Local Wake-Up behavior

Beside the remote Wake-Up, a Wake-Up of the TLE7259-2GE via the WK pin is possible. This type of wake-up event is called "Local Wake Up". A falling edge on the WK pin followed by a "Low" signal for  $t > t_{WK}$  results in a local Wake-Up (see **Figure 8**) and changes the operation mode to Stand-By mode.

In Stand-By mode the TxD pin indicates the source of the Wake-Up event. A strong pull-down on the pin TxD indicates a bus Wake-Up event (see **Figure 4**). The RxD pin signals if a Wake-Up event or the Power-Up event occurred. A "Low" signal on the RxD pin reports a local or bus Wake-Up event, a logical "High" signal on RxD indicates a Power-Up event.

### 4.8 Mode Transition via EN pin

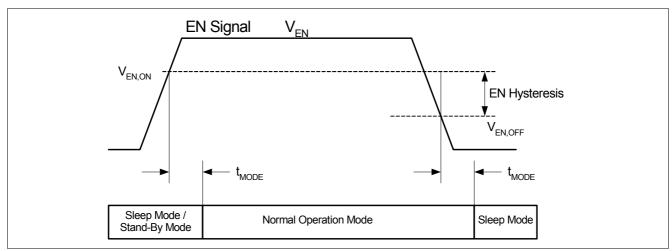

Figure 9 Mode Transition via EN pin

It is also possible to change from Sleep mode to Normal Operation mode by setting the EN pin to logical "High". This feature is useful if the external microcontroller is continuously powered, the microcontroller power-supply is not controlled by the INH pin. The EN pin has an integrated pull-down resistor to ensure the device remains in Sleep or Stand-By mode even if the voltage on the EN pin is floating. The EN pin has an integrated hysteresis (see Figure 9).

A transition from logical "High" to logical "Low" on the EN pin changes the operation mode from Normal Operation mode to Sleep mode. If the TLE7259-2GE is already in Sleep mode, changing the EN from "Low" to "High" results into a mode change from Sleep mode to Normal Operation mode. If the device is in Stand-By mode a change from "Low" to "High" on the EN pin changes the mode to Normal Operation mode, as well (see Figure 4).

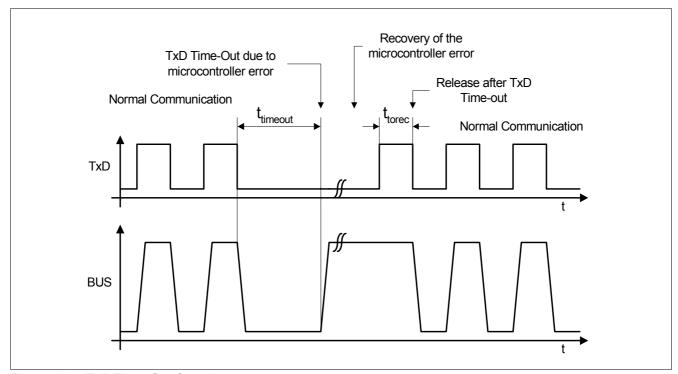

#### 4.9 TxD Time Out function

If the TxD signal is dominant for a time  $t > t_{\text{timeout}}$  the TxD time-out function deactivates the transmission of the LIN signal to the bus and disables the output stage. This is realized to prevent the bus from being blocked by a permanent "Low" signal on the TxD pin, caused by an error on the external microcontroller (see **Figure 10**).

The transmission is released again, after a rising edge at the pin TxD has been detected.

Figure 10 TxD Time-Out function

### 4.10 Over Temperature protection

The TLE7259-2GE has an integrated over temperature sensor to protect the device against thermal overstress on the output stage. In case of an over temperature event, the temperature sensor will disable the output stage (see **Figure 1**). An over temperature event will not cause any mode change and won't be indicated by the RxD pin or the TxD pin. When the junction temperature falls below the thermal shut down level  $T_{\rm J} < T_{\rm jSD}$ , the output stage is re-enabled and data communication can start again on the LIN bus. A 10°C hysteresis avoids toggling during the temperature shut down.

### 4.11 3.3 V and 5 V Logic Capability

The TLE7259-2GE can be used for 3.3 V and 5 V microcontrollers. The inputs and the outputs are capable to operate with both voltage levels. The RxD output must have an external pull-up resistor to the microcontroller supply to define the output voltage level.

#### **BUS Short to GND Feature**

The TLE7259-2GE has a feature implemented to protect the battery from running out of charge in case the LIN bus is shorted to GND.

In this failure case a normal master termination, a 1 k $\Omega$  resistor and diode between the LIN bus and the power supply  $V_S$ , would cause a constantly drawn current even in Sleep mode. The resulting resistance of this short to GND is lower than 1 k $\Omega$ . To avoid this current during a generator off state, like in a parked car, the TLE7259-2GE has a bus short to GND feature implemented, which is activated in Sleep mode.

This feature is only applicable, if the master termination of the LIN bus is connected to the INH pin, instead of being connected to the power supply  $V_S$  (see **Figure 15** and **Figure 16**). Internally, the 30 k $\Omega$  path is also switched off from the power supply  $V_S$  (see **Figure 1**).

A separate Master Termination Switch is implemented at the pin BUS, to avoid a voltage drop on the recessive level of LIN bus, in case of a dominant level or a short to ground on at the LIN bus.

#### 4.12 LIN Specifications 1.2, 1.3, 2.0 and 2.1

The device fulfills the Physical Layer Specification of LIN 1.2, 1.3, 2.0 and 2.1.

The differences between LIN specification 1.2 and 1.3 is mainly the physical layer specification. The reason was to improve the compatibility between the nodes.

The LIN specification 2.0 is a super set of the 1.3 version. The 2.0 version offers new features. However, it is possible to use the LIN 1.3 slave node in a 2.0 node cluster, as long as the new features are not used. Vice versa it is possible to use a LIN 2.0 node in the 1.3 cluster without using the new features.

In terms of the physical layer the LIN 2.1 Specification doesn't include any changes and is fully compliant to the LIN Specification 2.0.

LIN 2.1 is the latest version of the LIN specification, released in December 2006.

Data Sheet 16 Rev. 1.0, 2007-11-12

**General Product Characteristics**

#### 5 General Product Characteristics

### 5.1 Absolute Maximum Ratings

Table 3 Absolute Maximum Ratings Voltages, Currents and Temperatures<sup>1)</sup>

All voltages with respect to ground; positive current flowing into pin; (unless otherwise specified)

| Pos.   | Parameter                                                     | Symbol              | Limit Va      | lues          | Unit | Remarks                                                   |  |

|--------|---------------------------------------------------------------|---------------------|---------------|---------------|------|-----------------------------------------------------------|--|

|        |                                                               |                     | Min.          | Max.          |      |                                                           |  |

| Voltag | es                                                            | +                   |               | <del></del>   | +    |                                                           |  |

| 5.1.1  | Battery supply voltage                                        | $V_{\rm S}$         | -0.3          | 40            | V    | LIN Spec 2.1 Param. 10                                    |  |

| 5.1.2  | Bus and WK input voltage                                      |                     |               |               |      | _                                                         |  |

|        | versus GND                                                    | $V_{BUS,G}$         | -40           | 40            | V    |                                                           |  |

|        | versus V <sub>S</sub>                                         | V <sub>BUS,Vs</sub> | -40           | 40            | V    |                                                           |  |

| 5.1.3  | Logic voltages at EN, TxD, RxD                                | V <sub>logic</sub>  | -0.3          | 5.5           | V    | _                                                         |  |

| 5.1.4  | INH Voltage                                                   |                     |               |               |      | _                                                         |  |

|        | versus GND                                                    | $V_{INH,G}$         | -0.3          | 40            | V    |                                                           |  |

|        | versus V <sub>S</sub>                                         | $V_{INH, Vs}$       | -40           | 0.3           | V    |                                                           |  |

| Curre  | nts                                                           |                     | <u> </u>      | <u> </u>      |      |                                                           |  |

| 5.1.5  | Output current at INH                                         | I <sub>INH</sub>    | -150          | 80            | mA   | 2)                                                        |  |

| Tempe  | eratures                                                      |                     | <del></del> ! | <del></del> ! | •    |                                                           |  |

| 5.1.6  | Junction temperature                                          | $T_{\rm j}$         | -40           | 150           | °C   | _                                                         |  |

| 5.1.7  | Storage temperature                                           | T <sub>s</sub>      | -55           | 150           | °C   | _                                                         |  |

| ESD R  | esistivity                                                    |                     |               |               | -    |                                                           |  |

| 5.1.8  | Electrostatic discharge voltage at $V_S$ , Bus, WK versus GND | V <sub>ESD</sub>    | -6            | 6             | kV   | Human Body Model (100pF via 1.5 $k\Omega$ ) <sup>3)</sup> |  |

| 5.1.9  | Electrostatic discharge voltage all pins                      | V <sub>ESD</sub>    | -2            | 2             | kV   | Human Body Model (100pF via 1.5 $k\Omega$ ) <sup>3)</sup> |  |

<sup>1)</sup> Not subject to production test, specified by design

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

<sup>2)</sup> Output current is internally limited to -150 mA

<sup>3)</sup> ESD susceptibility HBM according to EIA / JESD 22-A 114

#### **General Product Characteristics**

### 5.2 Functional Range

Table 4 Operating Range

| Pos.  | Parameter                                   | Symbol              | Limit \ | /alues   |          | Unit | Remarks                       |

|-------|---------------------------------------------|---------------------|---------|----------|----------|------|-------------------------------|

|       |                                             |                     | Min.    | Тур.     | Max.     |      |                               |

| Suppl | y voltages                                  | 1                   |         | <u> </u> | <u> </u> |      |                               |

| 5.2.1 | Extended Supply Voltage Range for Operation | V <sub>S(ext)</sub> | 5       | _        | 40       | V    | Parameter deviations possible |

| 5.2.1 | Supply Voltage range for Normal Operation   | V <sub>S(nor)</sub> | 7       | -        | 27       | V    | LIN Spec 2.1 Param. 10        |

| Therm | al parameters                               | 1                   |         | <u> </u> | <u> </u> |      |                               |

| 5.2.2 | Junction temperature                        | $T_{\rm i}$         | -40     | _        | 150      | °C   | 1)                            |

<sup>1)</sup> Not subject to production test, specified by design

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 5.3 Thermal Characteristics

Table 5 Thermal Resistance<sup>1)</sup>

| Pos.  | Parameter                   | Symbol Limit Values |      |                |      | Unit | Remarks           |

|-------|-----------------------------|---------------------|------|----------------|------|------|-------------------|

|       |                             |                     | Min. | Тур.           | Max. |      |                   |

| Therm | nal Resistance              |                     |      | <del>- !</del> |      |      | <u>'</u>          |

| 5.3.3 | Junction to Soldering Point | $R_{thJSP}$         | _    | -              | 25   | K/W  | measured on pin 5 |

| 5.3.4 | Junction ambient            | $R_{thJA}$          | _    | 130            | _    | K/W  | 2)                |

| Therm | nal Shutdown Junction Te    | emperature          | )    |                | "    |      | <u>'</u>          |

| 5.3.5 | Thermal shutdown temp.      | $T_{\rm jSD}$       | 150  | 175            | 190  | °C   | _                 |

| 5.3.6 | Thermal shutdown hyst.      | $\Delta T$          | _    | 10             | _    | K    | _                 |

<sup>1)</sup> Not subject to production test, specified by design

Data Sheet 18 Rev. 1.0, 2007-11-12

<sup>2)</sup> JESD 51-2, 51-3, FR4 76,2 mm x 114,3 mm x 1,5 mm, 70  $\mu$ m Cu, minimal footprint, Ta = 27°C

### **6** Electrical Characteristics

#### **6.1** Functional Device Characteristics

#### **Table 6** Electrical Characteristics

| Pos.   | Parameter                                            | Symbol                    | Limit | Values |      | Uni | Remarks                                                                            |  |

|--------|------------------------------------------------------|---------------------------|-------|--------|------|-----|------------------------------------------------------------------------------------|--|

|        |                                                      |                           | Min.  | Тур.   | Max. | t   |                                                                                    |  |

| Curre  | nt Consumption                                       | !                         | 1     |        |      | -   |                                                                                    |  |

| 6.1.1  | Current consumption at $V_{\rm S}$                   | I <sub>S,rec</sub>        | 0.5   | 1.1    | 3.0  | mA  | Recessive state, without $R_L$ ;<br>$V_S$ = 13.5 V;<br>$V_{TxD}$ = "High"          |  |

| 6.1.2  | Current consumption at $V_S$<br>Dominate State       | I <sub>S,dom</sub>        | _     | 1.5    | 5.0  | mA  | Dominant state, without $R_L$ ; $V_S = 13.5 \text{ V}$ ; $V_{TXD} = 0 \text{ V}$   |  |

| 6.1.3  | Current consumption at $V_{\rm S}$ in sleep mode     | I <sub>S,sleep</sub>      | _     | 5      | 12   | μΑ  | Sleep mode.<br>$V_{\rm S}$ = 18 V;<br>$V_{\rm WK}$ = $V_{\rm S}$ = $V_{\rm BUS}$ ; |  |

| 6.1.4  | Current consumption at $V_S$ in sleep mode           | I <sub>S</sub> ,sleep,typ | _     | _      | 10   | μΑ  | Sleep mode, $T_j$ < 85 °C $V_S$ = 13.5 V; $V_{WK}$ = $V_S$ = $V_{BUS}$             |  |

| 6.1.5  | Current consumption in sleep mode bus shorted to GND | I <sub>S,lkg,SC_GND</sub> | _     | 45     | 100  | μΑ  | Sleep mode, $V_{\rm S}$ = 13.5 V; $V_{\rm BUS}$ =0V                                |  |

| Receiv | er Output: RxD                                       | 1                         |       |        | -    |     |                                                                                    |  |

| 6.1.6  | HIGH level leakage current                           | I <sub>RD,H,leak</sub>    | -5    | -      | 5    | μA  | $V_{\text{RxD}}$ = 5V; $V_{\text{BUS}}$ = $V_{\text{S}}$                           |  |

| 6.1.7  | LOW level output current                             | $I_{RD,L}$                | 1.3   | -      | 10   | mA  | $V_{\text{RxD}} = 0.9 \text{V}, \ V_{\text{BUS}} = 0 \text{V}$                     |  |

| Transn | nission Input: TxD                                   |                           | I     |        |      |     |                                                                                    |  |

| 6.1.8  | HIGH level input voltage range                       | $V_{TD,H}$                | 2     | -      | 5.5  | V   | Recessive state                                                                    |  |

| 6.1.9  | Input hysteresis                                     | V <sub>TD,hys</sub>       | 150   | 300    | 450  | mV  | 1)                                                                                 |  |

| 6.1.10 | LOW level input voltage range                        | $V_{TD,L}$                | -0.3  | _      | 0.8  | V   | Dominant state                                                                     |  |

| 6.1.11 | Pull-down resistance                                 | R <sub>TD</sub>           | 100   | 350    | 800  | kΩ  | $V_{TxD}$ = High                                                                   |  |

| 6.1.12 | Dominant current standby mode after Wake-Up          | I <sub>TD,L</sub>         | 1.5   | 3      | 10   | mA  |                                                                                    |  |

| 6.1.13 | Input capacitance                                    | Ci                        | _     | 5      | _    | pF  | 1)                                                                                 |  |

#### Table 6 Electrical Characteristics (cont'd)

| Pos.    | Parameter                                              | Symbol                 | Limit \                     | /alues                |                           | Uni | Remarks                                         |  |

|---------|--------------------------------------------------------|------------------------|-----------------------------|-----------------------|---------------------------|-----|-------------------------------------------------|--|

|         |                                                        |                        | Min.                        | Тур.                  | Max.                      | t   |                                                 |  |

| Enable  | e Input: EN                                            | I                      |                             | 11                    |                           | 1   |                                                 |  |

| 6.1.14  | HIGH level input voltage range                         | $V_{EN,ON}$            | 2                           | _                     | 5.5                       | V   | Normal Operation mode                           |  |

| 6.1.15  | LOW level input voltage range                          | $V_{EN,OFF}$           | -0.3                        | _                     | 0.8                       | V   | Sleep mode or Stand-By mode                     |  |

| 6.1.16  | Input hysteresis                                       | V <sub>EN,hys</sub>    | 150                         | 300                   | 450                       | mV  | 1)                                              |  |

| 6.1.17  | Pull-down resistance                                   | R <sub>EN</sub>        | 15                          | 30                    | 60                        | kΩ  | -                                               |  |

| 6.1.18  | Input capacitance                                      | Ci <sub>EN</sub>       | _                           | 5                     | _                         | pF  | 1)                                              |  |

| Inhibit | , Master Termination Output: I                         | NH                     | -!                          | •                     | *                         | *   |                                                 |  |

| 6.1.19  | Inhibit R <sub>on</sub> resistance                     | $R_{INH,on}$           | 22                          | 36                    | 50                        | Ω   | I <sub>INH</sub> = -15 mA                       |  |

| 6.1.20  | Maximum INH output current                             | I <sub>INH</sub>       | -150                        | -110                  | -40                       | mA  | V <sub>INH</sub> = 0 V                          |  |

| 6.1.21  | Leakage current                                        | I <sub>INH,Ik</sub>    | -5.0                        | -                     | 5.0                       | μΑ  | Sleep mode;<br>V <sub>INH</sub> = 0 V           |  |

| Wake    | Input: WK                                              |                        |                             | 1                     | 1                         |     |                                                 |  |

| 6.1.22  | High level input voltage                               | $V_{\mathrm{WK,H}}$    | <i>V</i> <sub>S</sub> - 1 V | _                     | V <sub>S</sub> + 3 V      | V   | tested $V_{\rm S}$ = 13.5 V;                    |  |

| 6.1.23  | Low level input voltage                                | $V_{WK,L}$             | -0.3                        | _                     | V <sub>S</sub> - 4 V      | V   | tested $V_{\rm S}$ = 13.5 V;                    |  |

| 6.1.24  | Pull-up current                                        | I <sub>WK,PU</sub>     | -60                         | -20                   | -3                        | μΑ  | _                                               |  |

| 6.1.25  | High level leakage current                             | I <sub>WK,H,leak</sub> | -5                          | _                     | 5                         | μА  | $V_S = 0 \text{ V};$<br>$V_{WK} = 40 \text{ V}$ |  |

| 6.1.26  | Dominant time for Wake-Up                              | t <sub>WK</sub>        | 30                          | _                     | 150                       | μS  | _                                               |  |

| 6.1.27  | Input Capacitance                                      | Ci <sub>WK</sub>       | _                           | 15                    | _                         | рF  | 1)                                              |  |

| Bus R   | eceiver: BUS                                           | 1                      | -                           | 1                     | 1                         | 1   |                                                 |  |

| 6.1.28  | Receiver threshold voltage, recessive to dominant edge | $V_{ m th\_dom}$       | 0.4 × V <sub>S</sub>        | 0.45 × V <sub>S</sub> | _                         | V   | _                                               |  |

| 6.1.29  | Receiver dominant state                                | V <sub>BUSdom</sub>    | V <sub>S</sub> - 40 V       | _                     | 0.4 × V <sub>S</sub>      | V   | LIN Spec 2.1 (Par. 17) <sup>2)</sup>            |  |

| 6.1.30  | Receiver threshold voltage, dominant to recessive edge | V <sub>th_rec</sub>    | -                           | 0.55 × V <sub>S</sub> | 0.6 × V <sub>S</sub>      | V   | -                                               |  |

| 6.1.31  | Receiver recessive state                               | V <sub>BUSrec</sub>    | 0.6 × V <sub>S</sub>        | _                     | 1.15 x<br>V <sub>s</sub>  | V   | LIN Spec 2.1 (Par. 18) 3)                       |  |

| 6.1.32  | Receiver center voltage                                | V <sub>BUS_CNT</sub>   | 0.475<br>× V <sub>S</sub>   | 0.5 × V <sub>S</sub>  | 0.525<br>× V <sub>S</sub> | V   | LIN Spec 2.1 (Par. 19) 4)                       |  |

| 6.1.33  | Receiver hysteresis                                    | V <sub>HYS</sub>       | 0.07 × V <sub>S</sub>       | 0.12 × V <sub>S</sub> | 0.175<br>× V <sub>S</sub> | ٧   | LIN Spec 2.1 (Par. 20) 5)                       |  |

| 6.1.34  | Wake-Up threshold voltage                              | $V_{\rm BUS,wk}$       | 0.40 × V <sub>S</sub>       |                       | 0.6 × V <sub>S</sub>      | V   | _                                               |  |

| 6.1.35  | Dominant time for bus Wake-<br>Up                      | t <sub>WK,bus</sub>    | 30                          | _                     | 150                       | μS  | _                                               |  |

### Table 6 Electrical Characteristics (cont'd)

| Pos.   | Parameter                                                                  | Symbol                                | Limit '                        | Values      |                                    | Uni         | Remarks                                                                                                                                                                |  |

|--------|----------------------------------------------------------------------------|---------------------------------------|--------------------------------|-------------|------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        |                                                                            |                                       | Min. Typ. Max                  |             | Max.                               | t           |                                                                                                                                                                        |  |

| Bus Ti | ransmitter BUS                                                             |                                       |                                |             |                                    |             |                                                                                                                                                                        |  |

| 6.1.36 | Bus recessive output voltage                                               | $V_{\mathrm{BUS,ro}}$                 | 0.8 ×<br><i>V</i> <sub>S</sub> | _           | V <sub>S</sub>                     | V           | $V_{\text{TxD}}$ = high Level                                                                                                                                          |  |

| 6.1.37 | Bus dominant output voltage maximum load                                   | $V_{BUS,do}$                          | -<br>-<br>-                    | -<br>-<br>- | 1.2<br>0.2 x V <sub>S</sub><br>2.0 | V<br>V<br>V | $V_{TxD}$ = 0 V; $R_L$ = 500 Ω<br>6.0 ≤ $V_S$ ≤ 7.3 V;<br>7.3 < $V_S$ ≤ 10 V;<br>10 < $V_S$ ≤ 18 V;<br>(see Figure 12)                                                 |  |

| 6.1.38 | Bus short circuit current                                                  | I <sub>BUS_LIM</sub>                  | 40                             | 100         | 150                                | mA          |                                                                                                                                                                        |  |

| 6.1.39 | Leakage current                                                            | I <sub>BUS_NO_GN</sub>                | -1                             | -0.5        | -                                  | mA          | $V_{\rm S}$ = 0 V; $V_{\rm BUS}$ = -12 V;<br>LIN Spec 2.1 (Par. 15)                                                                                                    |  |

| 6.1.40 | Leakage current                                                            | I <sub>BUS_NO_BAT</sub>               | _                              | 1           | 8                                  | μΑ          | $V_{\rm S}$ = 0 V; $V_{\rm BUS}$ = 18 V;<br>LIN Spec 2.1 (Par. 16)                                                                                                     |  |

| 6.1.41 | Leakage current                                                            | I <sub>BUS_PAS_dom</sub>              | -1                             | -0.5        | _                                  | mA          | $V_{\rm S}$ = 18 V; $V_{\rm BUS}$ = 0 V;<br>LIN Spec 2.1 (Par. 13)                                                                                                     |  |

| 6.1.42 | Leakage current                                                            | I <sub>BUS_PAS_rec</sub>              | _                              | 1           | 20                                 | μΑ          | $V_{\rm S}$ = 8 V; $V_{\rm BUS}$ = 18 V;<br>LIN Spec 2.1 (Par. 14)                                                                                                     |  |

| 6.1.43 | Bus pull-up resistance                                                     | R <sub>slave</sub>                    | 20                             | 30          | 47                                 | kΩ          | Normal mode<br>LIN Spec 2.1 (Par. 26)                                                                                                                                  |  |

| 6.1.44 | LIN output current                                                         | I <sub>BUS</sub>                      | -60                            | -30         | -5                                 | μΑ          | Sleep mode $V_{\rm S}$ = 13.5V $V_{\rm EN}$ = 0V                                                                                                                       |  |

| 6.1.45 | Input Capacitance                                                          | Ci <sub>BUS</sub>                     |                                | 15          | _                                  | рF          | 1)                                                                                                                                                                     |  |

| Dynan  | nic Transceiver Characteristic                                             | s: BUS                                |                                |             |                                    |             |                                                                                                                                                                        |  |

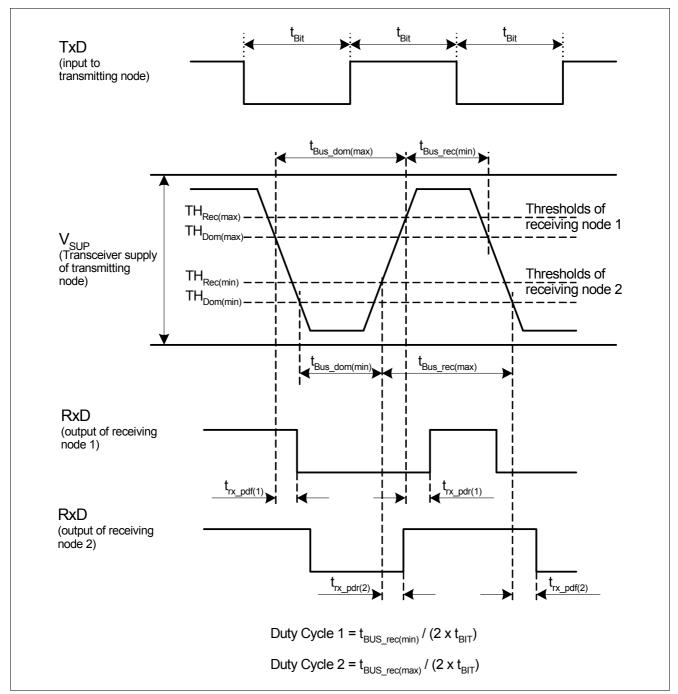

| 6.1.46 | Propagation delay LIN bus to RxD Dominant to RxD Low Recessive to RxD High | $t_{ m rx\_pdf}$ $t_{ m rx\_pdr}$     | _                              | 1           | 6                                  | μs<br>μs    | LIN Spec 2.1 (Par. 31)<br>$R_{\rm RxD}$ = 2.4 k $\Omega$ ;<br>$C_{\rm RxD}$ = 20 pF                                                                                    |  |

| 6.1.47 | Receiver delay symmetry                                                    | t <sub>rx_sym</sub>                   | -2                             | _           | 2                                  | μS          | LIN Spec 2.1 (Par. 32)<br>$t_{\text{rx\_sym}} = t_{\text{rx\_pdr}} t_{\text{rx\_pdr}};$<br>$R_{\text{RxD}} = 2.4 \text{ k}\Omega;$<br>$C_{\text{RxD}} = 20 \text{ pF}$ |  |

| 6.1.48 | Delay time for mode change                                                 | $t_{MODE}$                            | _                              | _           | 150                                | μS          | <sup>1)</sup> See <b>Figure 5</b>                                                                                                                                      |  |

| 6.1.49 | TxD dominant time out                                                      | $t_{\rm timeout}$                     | 6                              | 12          | 20                                 | ms          | $V_{TxD} = 0 \text{ V}$                                                                                                                                                |  |

| 6.1.50 | TxD dominant time out recovery time                                        | t <sub>torec</sub>                    | _                              | _           | 15                                 | μS          | 1)                                                                                                                                                                     |  |

| 6.1.51 | EN toggling to enter the flash mode                                        | t <sub>fl1</sub>                      | 25                             | 35          | 50                                 | μS          | <sup>1)</sup> See <b>Figure 6</b>                                                                                                                                      |  |

| 6.1.52 | TxD time for flash activation                                              | $t_{\mathrm{fl2}}$ $t_{\mathrm{fl3}}$ | 5<br>10                        | _           | _                                  | μS          | <sup>1)</sup> See <b>Figure 6</b>                                                                                                                                      |  |

|        |                                                                            | $t_{fl4}$                             | 10                             | _           | _                                  |             |                                                                                                                                                                        |  |

#### Table 6 Electrical Characteristics (cont'd)

| Pos.   | Parameter                                      | Symbol | Limit Values |      |       | Uni | Remarks                                                                                                                                                                                                                                                              |

|--------|------------------------------------------------|--------|--------------|------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                |        | Min.         | Typ. | Max.  | t   |                                                                                                                                                                                                                                                                      |

| 6.1.53 | Duty cycle D1<br>(for worst case at 20 kBit/s) | D1     | 0.396        | -    | -     |     | duty cycle $1^6$ ) $TH_{Rec}(max) = 0.744 \times V_S;$ $TH_{Dom}(max) = 0.581 \times V_S;$ $V_S = 7.0 \dots 18 V;$ $t_{bit} = 50 \mu S;$ D1 = $t_{bus\_rec(min)}/2 t_{bit};$ LIN Spec 2.1 (Par. 27)                                                                  |

| 6.1.54 | Duty cycle D2<br>(for worst case at 20 kBit/s) | D2     | -            | -    | 0.581 |     | duty cycle $2^{6}$ )  TH <sub>Rec</sub> (min)= $0.422 \times V_S$ ;  TH <sub>Dom</sub> (min)= $0.284 \times V_S$ $V_S = 7.6 \dots 18 \text{ V}$ ; $t_{\text{bit}} = 50 \mu \text{s}$ ;  D2 = $t_{\text{bus\_rec(max)}} / 2 t_{\text{bit}}$ ;  LIN Spec 2.1 (Par. 28) |

- 1) Not subject to production test, specified by design

- 2) Minimum limit specified by design

- 3) Maximum limit specified by design

- 4)  $V_{\mathrm{BUS\_CNT}} = (V_{\mathrm{th\_dom}} V_{\mathrm{th\ rec}})/2;$

- 5)  $V_{\text{HYS}} = V_{\text{BUSrec}} V_{\text{BUSdom}}$

- 6) Bus load concerning LIN Spec 2.1:

$$\begin{array}{l} {\rm Load~1=1~nF~/~1~k\Omega} = C_{BUS} \, / \, R_{BUS} \\ {\rm Load~2=6.8~nF~/~660~\Omega} = C_{BUS} \, / \, R_{BUS} \\ {\rm Load~3=10~nF~/~500~\Omega} = C_{BUS} \, / \, R_{BUS} \\ \end{array}$$

### 6.2 Diagrams

Figure 11 Simplified test circuit for dynamic characteristics

Figure 12 Simplified test circuit for static characteristics

Figure 13 Timing diagram for dynamic characteristics

### 7 Application Information

#### 7.1 ESD Robustness according to IEC61000-4-2

Test for ESD robustness according to IEC61000-4-2 "Gun test" (150 pF, 330  $\Omega$ ) have been performed. The results and test conditions are available in a separate test report.

Table 7 ESD Robustness according to IEC61000-4-2

| Performed Test                                                          | Result | Unit | Remarks                      |

|-------------------------------------------------------------------------|--------|------|------------------------------|

| Electrostatic discharge voltage at pin $V_{\mathcal{S}}$ BUS versus GND | ≥ 11   | kV   | <sup>1)</sup> Positive pulse |

| Electrostatic discharge voltage at pin $V_{\mathcal{S}}$ BUS versus GND | ≤ -11  | kV   | <sup>1)</sup> Negative pulse |

| Electrostatic discharge voltage at pin WK versus GND                    | ≥ 9    | kV   | <sup>1)</sup> Positive pulse |

| Electrostatic discharge voltage at pin WK versus GND                    | ≤ -9   | kV   | <sup>1)</sup> Negative pulse |

<sup>1)</sup> ESD susceptibility "ESD GUN" according LIN EMC 1.3 Test Specification, Section 4.3. (IEC 61000-4-2) -Tested by external test house.

### 7.2 Pin Compatibility to other LIN Transceivers

The LIN Transceiver TLE7259-2GE is pin and function compatible to the Single LIN Transceivers like the TLE7259G, the TLE7259-2GU and other single LIN Transceivers on the market. The TLE7259-2GE has no  $V_{\rm IO}$  supply pin. Therefore the TLE7259-2GE needs a pull-up resistor to the external microcontroller supply. The TLE7259-2GE can also be used on a PCB design for the Twin LIN TLE7269G. Since the TLE7269G doesn't need a pull-up resistor on the RxD pin, a pull-up resistor to the external microcontroller needs to be added to get the same functionality.

Figure 14 Pin configuration TLE7259-2GE, TLE7259-2GU, TLE7259G and TLE7269G

#### 7.3 Master Termination

To achieve the required timings for the dominant to recessive transition of the bus signal an additional external termination resistor of 1  $k\Omega$  is mandatory. It is recommended to place this resistor at the master node. To avoid reverse currents from the bus line into the battery supply line it is recommended to place a diode in series with the external pull-up. For small systems (low bus capacitance) the EMC performance of the system is supported by an additional capacitor of at least 1 nF at the master node (see **Figure 15** and **Figure 16**). The values for the Master Termination resistor and the bus capacitances influence the performance of the LIN network. They depend on the number of nodes inside the LIN network and on the parasitic cable capacitance of the LIN bus wiring.

### 7.4 External Capacitors

A capacitor of 10  $\mu$ F at the supply voltage input  $V_{\rm S}$  buffers the input voltage. In combination with the required reverse polarity diode this prevents the device from detecting a power down conditions in case of negative transients on the supply line (see **Figure 15** and **Figure 16**).

The 100 nF capacitor close to the  $V_{\rm S}$  pin of the TLE7259-2GE is required to get the best EMC performance.

Data Sheet 26 Rev. 1.0, 2007-11-12

### 7.5 Application Example

Figure 15 Simplified Application Circuit with Bus Short to GND Feature applied

Figure 16 Simplified application Circuit without Bus Short to GND Feature

**Package Outlines**

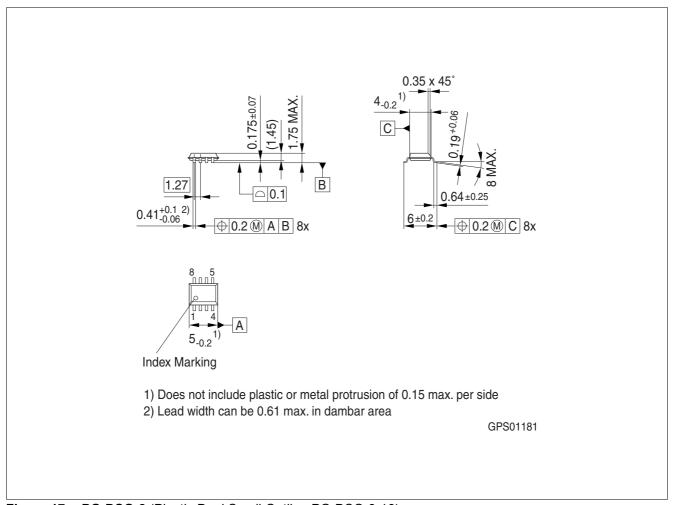

### 8 Package Outlines

Figure 17 PG-DSO-8 (Plastic Dual Small Outline PG-DSO-8-16)

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

# 9 Revision History

| Revision | Date       | Changes            |

|----------|------------|--------------------|

| 1.0      | 2007-11-06 | Data Sheet created |

|          |            |                    |

Edition 2007-11-12

Published by Infineon Technologies AG 81726 Munich, Germany © 2007 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.